近日,功率半導體器件領域的頂級會議IEEE International Symposium on Power Semiconductor Devices and ICs (ISPSD) 在日本熊本市舉行。北京大學集成電路學院兩篇高水平論文入選,向國際功率器件與功率集成電路領域的同行展示了北京大學最新的研究成果。這兩篇論文內容涉及GaN CMOS集成技術、SiC MOSFET可靠性物理研究。論文詳情如下:

1 高性能GaN CMOS集成技術

GaN CMOS邏輯電路是提升GaN功率芯片高頻特性的重要技術環節。然而,當前GaN p溝道場效應管 (p-FET) 的低電流密度問題限制了該技術的發展。針對這一問題,當前多數研究聚焦于器件溝道區域的優化,然而,p-FET低電流密度問題仍未得到有效解決。

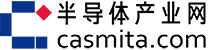

北京大學魏進團隊研究發現源極電阻對電流密度具有重要的影響。首先,研究團隊通過TCAD仿真發現源極電阻降低器件溝道處的有效柵壓,從而降低器件電流密度和增大器件的溝道電阻。為優化器件源極電阻從而提升電學性能,該團隊通過在器件接入區域插入一層Al0.7Ga0.3N,利用電離增強的方案有效降低器件的源極電阻。器件測試結果驗證了通過源極電阻工程可有效提升GaN p-FET電流密度,測試數據處于國際先進水平。相關成果以Engineering Extrinsic Resistance of E-Mode GaN p-FET towards Enhanced Current Density為題,發表于2025年國際功率半導體器件與集成電路研討會 (ISPSD), 文章第一作者是北京大學集成電路學院博士研究生段嘉霖,通訊作者是魏進研究員。

2 一種SiC MOSFET閾值電壓負漂移新機制研究

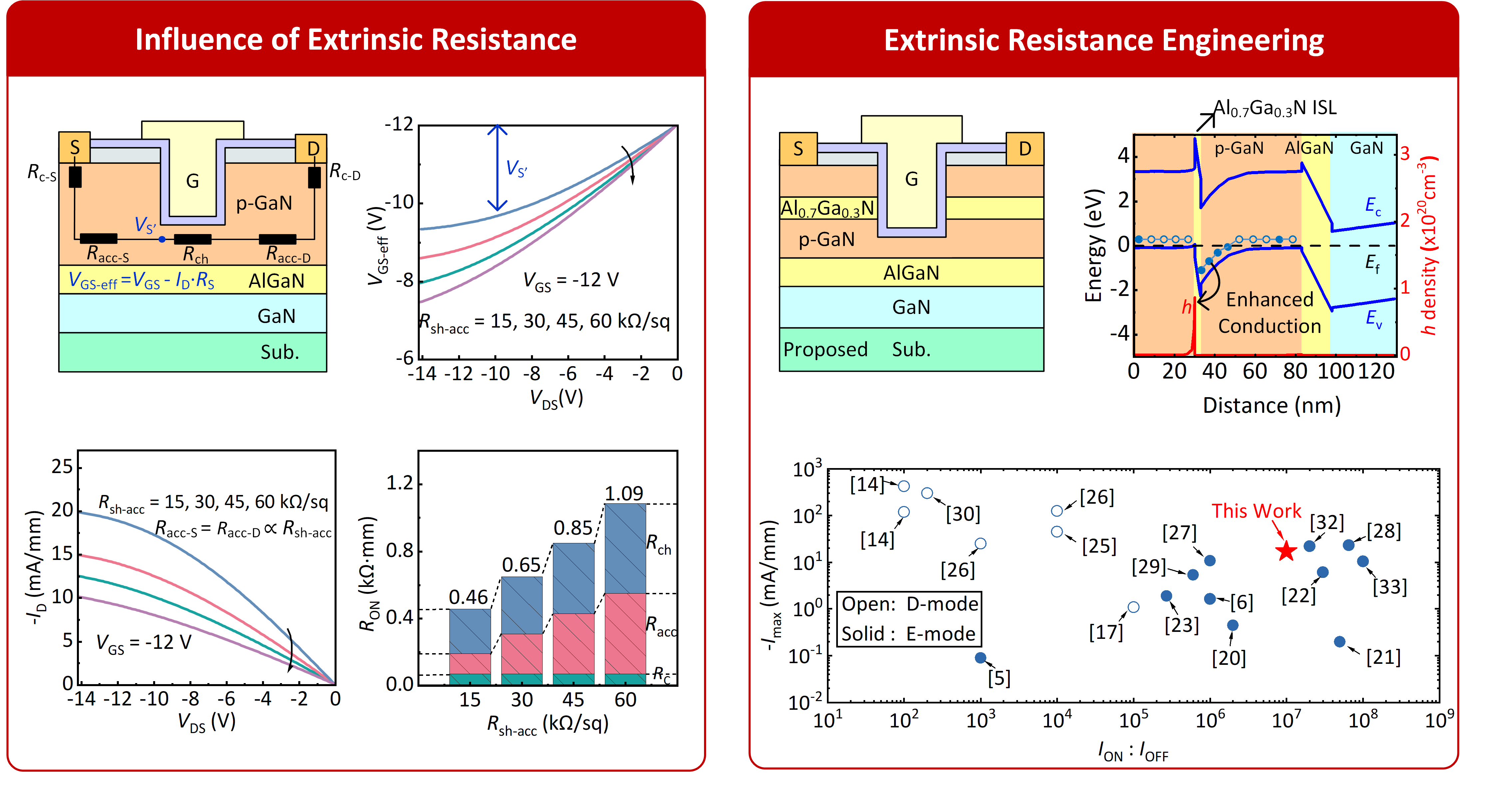

目前,SiC功率器件已在商業領域取得重大成功,但受限于當前的氧化工藝導致的較高界面陷阱,以及SiC/SiO?界面較小的帶隙差,使得閾值電壓Vth不穩定性成為SiC MOSFET的一個突出難題。在同步整流等實際應用場景中,續流二極管是必不可少的元件。一方面,相比反并聯肖特基勢壘二極管 (SBD),SiC MOSFET內置的體二極管憑借其更高的成本效益展現出顯著優勢。另一方面,為了抑制SiC MOSFET誤開啟現象,常使用負的柵極電壓將器件關斷。北京大學魏進研究員團隊通過深入研究首次發現,在體二極管導通狀態下施加負的柵極電壓關斷器件時,會引發顯著的閾值電壓負漂移現象。

針對這一重要發現,研究團隊創新性地提出了一種全新的物理機制:當體二極管導通時,p-well區會向JFET區注入大量空穴;在反向恢復過程中,這些空穴在漏極電場作用下加速流向源極,其中部分空穴被加在柵極上的負壓吸引,通過轟擊柵氧,在柵氧化層中積累固定的凈正電荷,導致閾值電壓漂移。該物理機制首次系統揭示了負柵偏壓誘導的閾值電壓不穩定性與體二極管導通的關聯性。該研究以Negative Gate Bias Induced Vth Instability in SiC MOSFET: Role of Body Diode Conduction為題,發表于2025年國際功率半導體器件與集成電路研討會ISPSD。文章的共同第一作者為北京大學/北京工業大學聯合培養碩士生王珮瑄和北京大學博士生勞云鴻,通訊作者為魏進研究員。

在材料科學領域,準確理解多原子系統的行為是一項基礎而又充滿挑戰的任務。以在鋰離子等高能量密度電池中發揮關鍵作用的鋰元素為例,精確預測鋰原子簇內部的能量和相互作用,對于推動下一代儲能技術至關重要。然而,隨著原子數量的增加,系統交互的復雜性呈指數級增長。雖然深度學習模型潛力巨大,但在材料科學領域,高質量數據的稀缺性和模型的“黑箱”特性限制了其應用。

來源:北京大學集成電路學院